思科近日宣布成功研发出首款量子网络纠缠芯片原型,并于当地时间5月6日在美国加利福尼亚州圣莫尼卡正式启用其量子实验室。

该公司指出,当前的量子处理器所拥有的量子比特数量仍处于三位数级别,即便按照最乐观的发展计划,到2030年也只能实现四位数的量子比特规模。然而,要运行实际应用所需的量子计算系统,其所需的量子比特数量远超当前水平,将达到数百万级,两者之间仍存在巨大差距。

思科强调,在传统计算技术发展过程中也曾面临类似挑战。当时,解决办法并非依赖于制造一台足够强大的单体计算机,而是通过建设网络基础设施,将大量小型计算节点连接为分布式系统。基于这一历史经验,思科认为,未来量子计算的发展路径也将趋向于横向扩展模式,即借助专用量子网络将多个量子处理器互联,从而构建一个更大规模的协同计算系统。

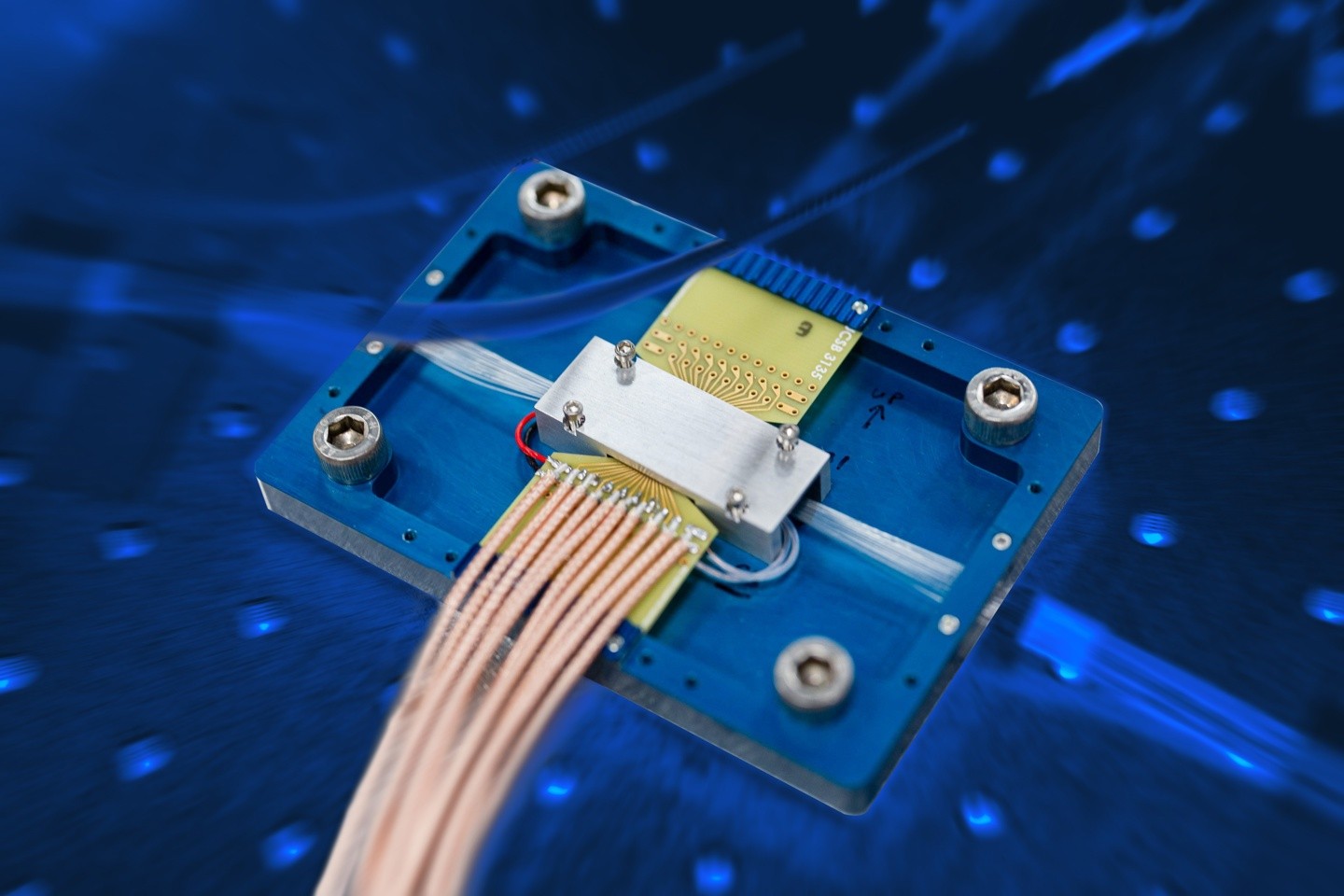

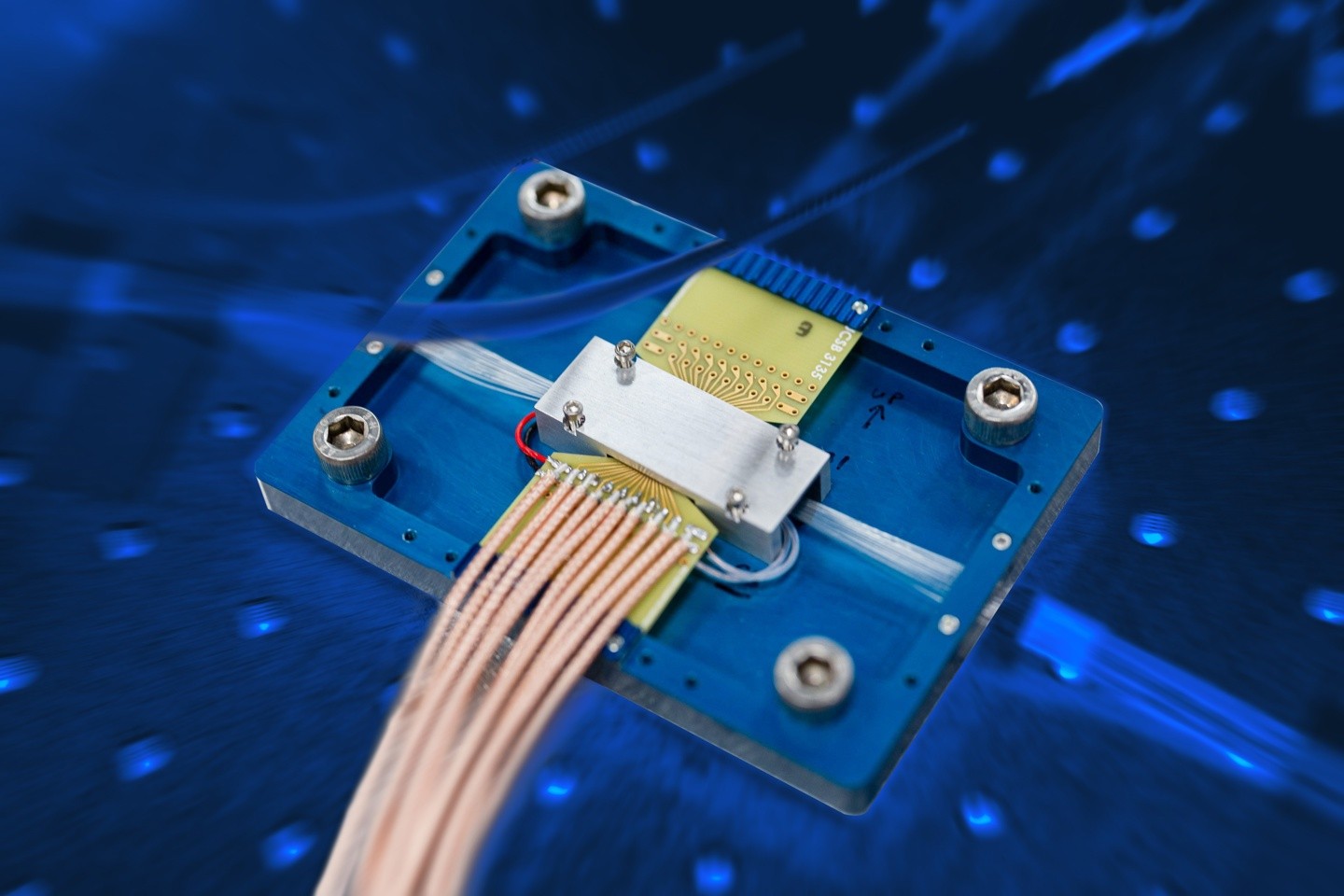

此次推出的量子网络纠缠芯片原型由思科与加州大学圣巴巴拉分校联合开发,利用一对纠缠光子之间的量子隐形传态实现高速通信。

该芯片采用硅基III-V半导体波导中的自发四波混频效应,在室温环境下即可作为微型光子集成电路稳定运行。芯片具备超过99%的保真度,功耗低于1毫瓦,并使用标准的1550纳米电信波长,因此可无缝集成到现有的光纤网络设施中。

据透露,该原型芯片在每个通道上每秒能产生超过100万对纠缠光子,整颗芯片的纠缠光子生成速率可达到每秒2亿对,为未来构建高效量子网络提供了重要基础。

本文属于原创文章,如若转载,请注明来源:思科发布量子网络芯片原型https://news.zol.com.cn/980/9807656.html